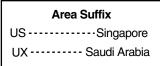

# JVC SERVICE MANUAL COMPACT COMPONENT SYSTEM

# **MX-K55V**

#### Contents

| Safety precautions            | 1-2  |

|-------------------------------|------|

| Preventing static electricity | 1-3  |

| Important for laser products  | 1-4  |

| Disassembly method            | 1-5  |

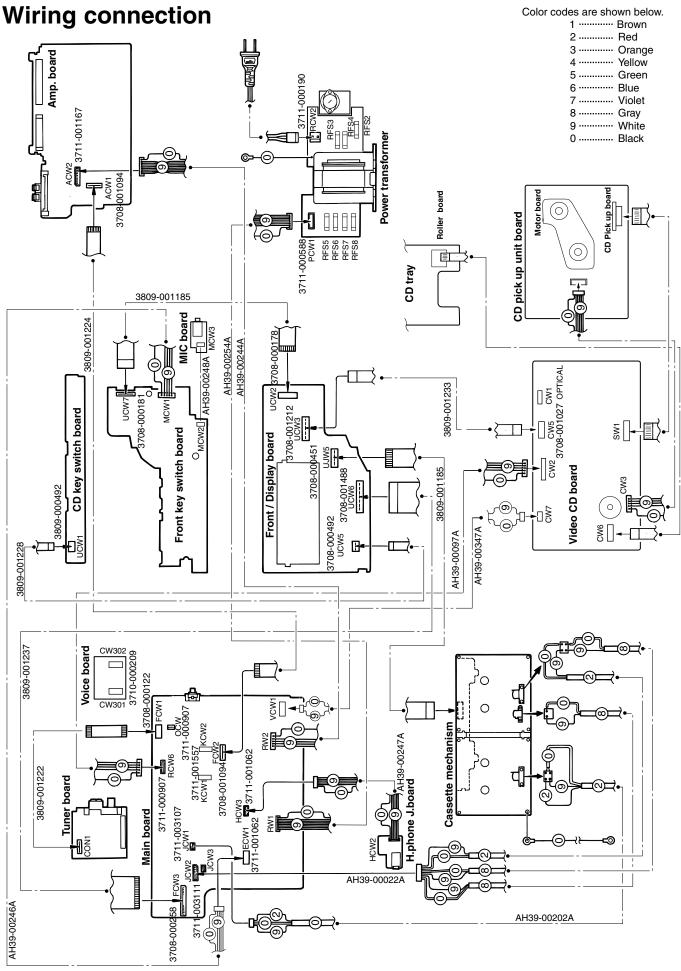

| Wiring connection             | 1-18 |

| Adjustment method             | 1-19 |

| Flow of functional operation     |

|----------------------------------|

| until TOC read 1-23              |

| Maintenance of laser pickup 1-24 |

| Replacement of laser pickup 1-24 |

| Troubleshooting 1-25             |

| Description of major ICs 1-33~52 |

### -Safety Precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

- 5. Leakage current check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

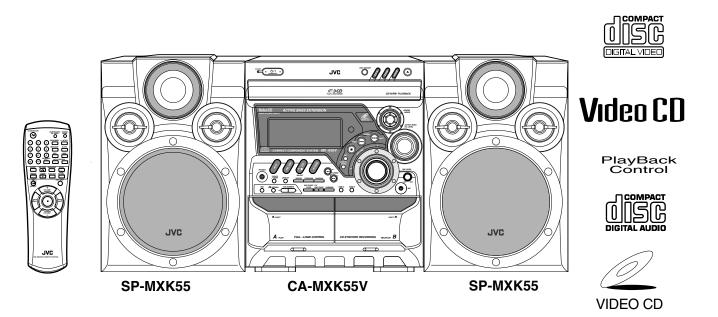

#### Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500  $\Omega$  10W resistor paralleled by a 0.15 $\mu$ F AC-type capacitor

between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and measure the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. Voltage measured any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

#### Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the parts that are printed over with black such as the resistor (--), diode (+-) and ICP (-) or identified by the " $\underline{\wedge}$ " mark nearby are critical for safety.

When replacing them, be sure to use the parts of the same type and rating as specified by the manufacturer. (Except the J&C version)

# Preventing static electricity

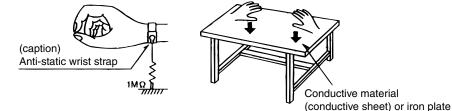

#### 1. Grounding to prevent damage by static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

#### 2. About the earth processing for the destruction prevention by static electricity

In the equipment which uses optical pick-up (laser diode), optical pick-up is destroyed by the static electricity of the work environment.

Be careful to use proper grounding in the area where repairs are being performed.

#### 2-1 Ground the workbench

Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

#### 2-2 Ground yourself

Use an anti-static wrist strap to release any static electricity built up in your body.

#### 3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

#### 4. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

#### Attention when CD mechanism assembly is decomposed

- \*Please refer to "Disassembly method" in the text for pick-up and how to detach the CD mechanism assembly.

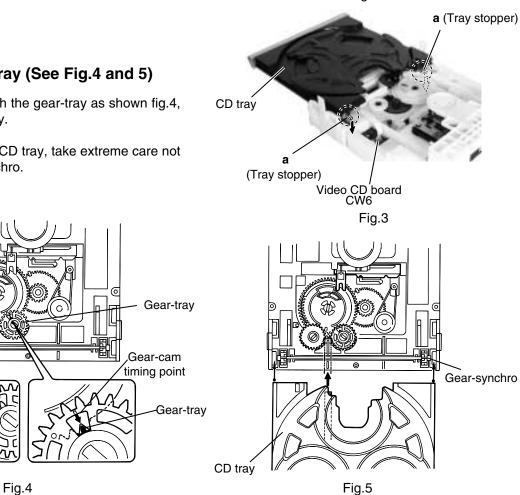

- Card wire 1. Remove the CD changer unit. Pickup unit 2. Remove the CD holder mechanism. connector CD holder 3. Solder is put up before the card wire is removed from the pickup unit mechanism connector on the CD mechanism assembly. Fig.1 (When the card wire is removed without putting up solder, the CD pick-up Card wire assembly might destroy.) 4. Please remove solder after connecting the card wire with the pickup unit connector when you install picking up in the substrate. Soldering Pickup unit

CD changer unit

connector Fig.2

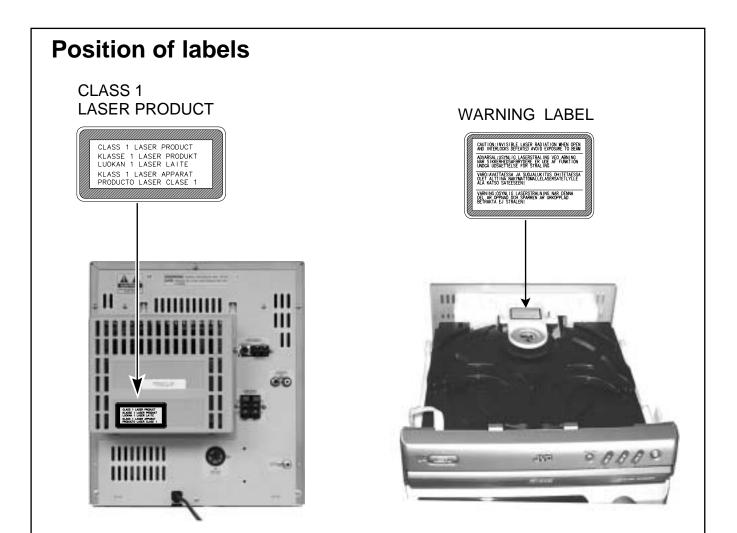

# Important for laser products

#### **1.CLASS 1 LASER PRODUCT**

- **2.DANGER :** Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION :** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

- **4.CAUTION :** The compact disc player uses invisible laserradiation and is equipped with safety switches whichprevent emission of radiation when the drawer is open and the safety interlocks have failed or are de feated. It is dangerous to defeat the safety switches.

- **5.CAUTION :** If safety switches malfunction, the laser is able to function.

- **6.CAUTION :** Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

A CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

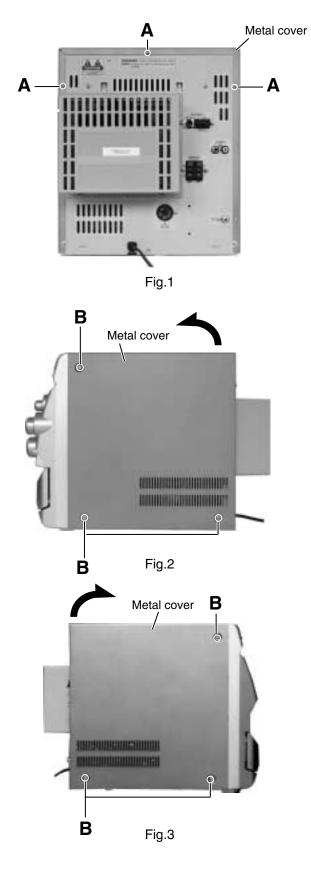

# **Disassembly method**

#### <Main body>

#### Removing the metal cover

#### (See Fig.1 to 3)

- 1. Remove the three screws **A** attaching the metal cover on the back of the body.

- 2. Remove the six screws **B** attaching the metal cover on both sides of the body.

- 3. Remove the metal cover from the body by lifting the rear part of the cover.

- ATTENTION: Do not break the front panel tab fitted to the metal cover.

#### MX-K55V

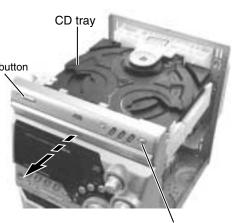

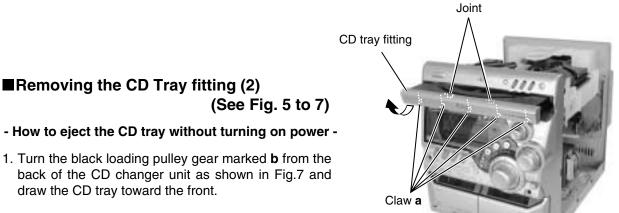

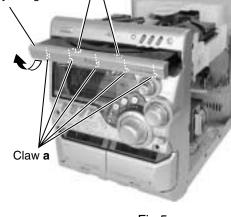

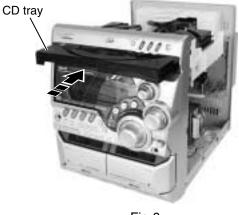

#### Removing the CD Tray fitting (1) (See Fig. 4 to 6)

- Prior to performing the following procedure, remove POWER button the metal cover.

- 1. Press the POWER button. Press the OPEN/CLOSE button to eject the CD tray.

- 2. After drawing the lower part of the tray fitting toward the front, remove the five claws a. Then, while moving the tray fitting upward, remove it.

- 3. Press the OPEN/CLOSE button to insert the tray.

**OPEN/CLOSE** button Fig.4

2. After drawing the lower part of the tray fitting toward the front, remove the five claws a. Then, while moving the tray fitting upward, remove it.

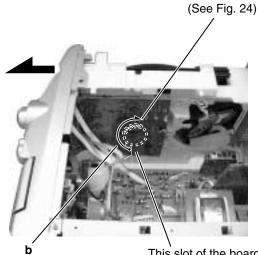

3. Push and insert the CD tray manually.

Fig.5

(Loading pulley gear)

This slot of the board.

Fig.7

Fig.6

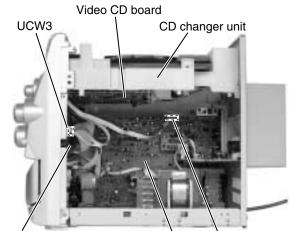

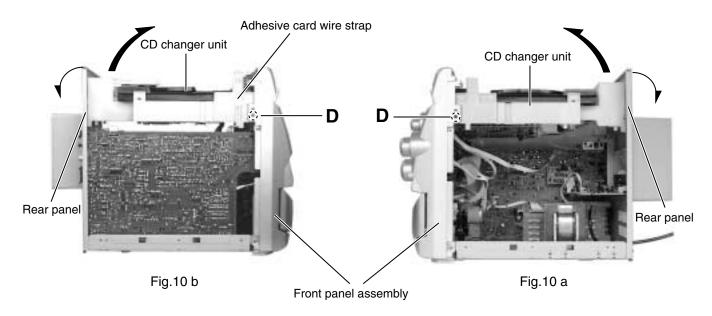

#### Removing the CD changer unit (See Fig.8 to 10)

- Prior to performing the following procedure, remove the metal cover.

- 1. Disconnect the card wire which is attached with adhesive to the left side of the CD changer unit.

- 2. Disconnect the card wire from connector UCW3 of the FL display and system control board on the back of the CD changer unit.

- 3. Disconnect the harness from connector RCW6 on the inner side of the main board in the body.

- 4. Remove the two screws **C** attaching the CD changer unit on the back of the body.

- 5. Remove the two screws **D** attaching the CD changer unit on the both side of the body.

- 6. Draw the CD changer unit upward from behind while pulling the rear panel outward.

FL display & system Main board RCW6 control board Fig.8

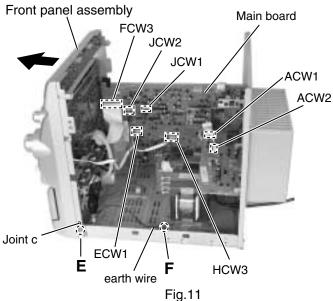

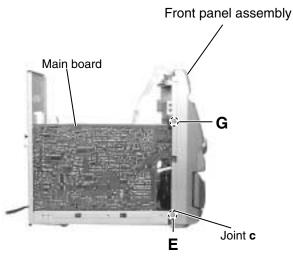

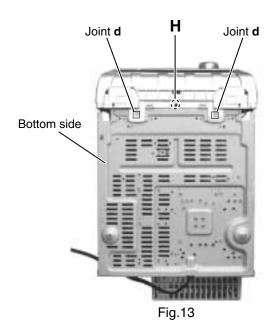

#### Removing the front panel assembly (See Fig.11 to 13)

- Prior to performing the following procedure, remove the metal cover and the CD changer unit.

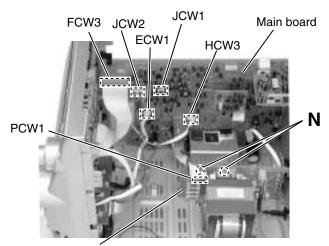

- 1. Disconnect the card wire from connector FCW3 and the harness from connector ECW1,JCW1, JCW2 and HCW3 on the inner side of the main board in the body.

- 2. Remove the two screws **E** attaching the front panel assembly on both sides of the body.

- 3. Remove the screw **F** attaching the earth terminal extending from the cassette mechanism assembly.

- 4. Remove the screw **G** attaching the front panel assembly and main board.

- 5. Remove the screw **H** attaching the front panel assembly on the bottom of the body.

- Release the two joints c on both sides and two joints d on the bottom of the body using a screwdriver.

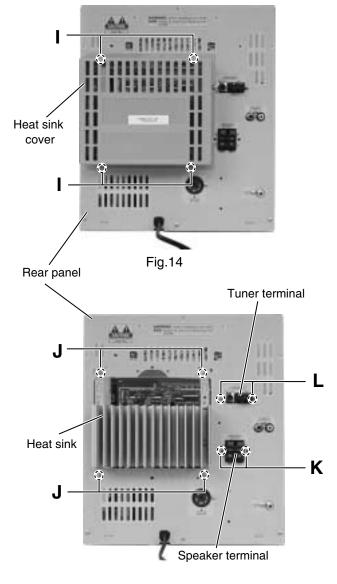

#### Removing the heat sink & Amp. board (See Fig.14 and 15)

- Prior to performing the following procedure, remove the metal cover and the CD changer unit.

- 1. Remove the four screws I attaching the heat sink cover on the back of the body. Remove the heat sink cover.

- 2. Remove the four screws **J** attaching the heat sink & Amp. board to the rear panel on the back of the body.

- 3. Remove the two screws **K** attaching the speaker terminal to the rear panel on the back of the body.

- 4. Disconnect the card wire from connector ACW1 & the harness from connector ACW2 on the Amp. board. (See Fig.11)

- 5. After moving the heat sink upward, remove the claws. Then pull out the heat sink & Amp. board inward.

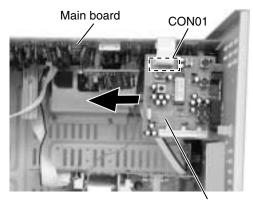

#### ■Removing the tuner pack (See Fig.15 to 16)

- Prior to performing the following procedure, remove the metal cover and CD changer unit.

- 1. Disconnect the card wire from connector CON01 on the tuner board.

- 2. Remove the two screws L attaching the tuner pack.

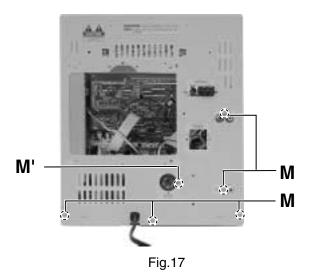

#### Removing the rear cover

(See Fig.17)

- Prior to performing the following procedure, remove the metal cover, CD changer unit, heat sink & Amp. board and tuner pack.

- 1. Remove the five screws **M**, and the screw **M**' attaching the rear panel.

Fig.15

#### MX-K55V

#### Removing the main board

(See Fig. 18)

- · Prior to performing the following procedure, remove the metal cover. CD changer unit.

- 1. Disconnect the card wire from connector FCW3 and the harness from connector ECW1, JCW1, JCW2 and HCW3 on the main board.

- 2. Disconnect the harness from connector PCW1 on the power transformer board.

- 3. Remove the screw G attaching the main board holder. (See Fig.12)

- 4. Remove the two screws **N** attaching the heat sink and bottom chassis.

Fig.18

Amp. board

Power transformer PCW1 R R RCW2 Power cord Fig.21

#### Removing the power IC

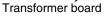

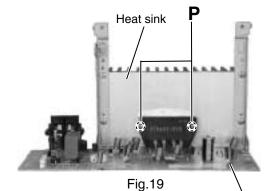

(See Fig.19 and 20)

- · Prior to performing the following procedure, remove the metal cover CD changer unit and heat sink & Amp. board.

- 1. Remove the two screws P attaching the power IC to the heat sink.

- 2. Unsolder the power IC solder point.

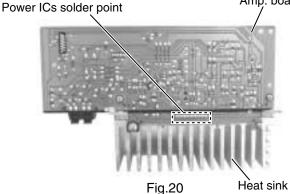

#### Removing the power transformer (See Fig. 21)

- · Prior to performing the following procedure, remove the metal cover, heat sink & Amp board, tuner pack and rear cover.

- 1. Disconnect the power cord from connector RCW2 of the power transformer board.

- 2. Disconnect the harness from connector PCW1 of the power transformer board.

- 3. Remove the four screws R attaching the power transformer.

#### <Front panel assembly>

• Prior to performing the following procedure, remove the metal cover, the CD changer unit and the front panel assembly.

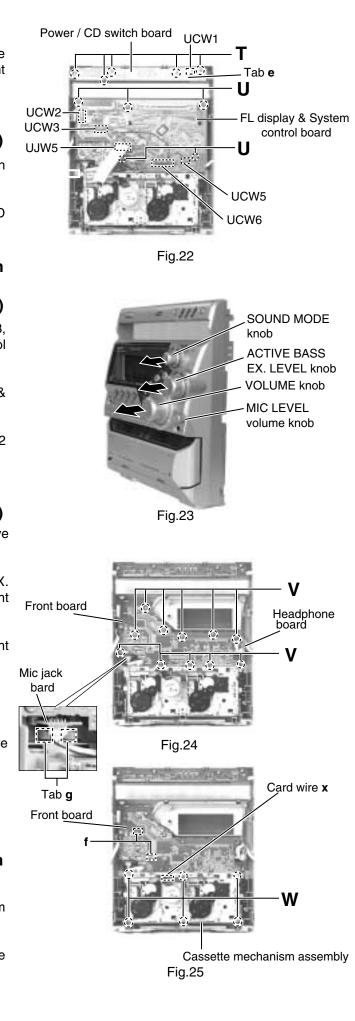

#### Removing the power / CD switch board (See Fig.22)

- 1. Disconnect the card wire from connector UCW1 on the power / CD switch board.

- 2. Remove the five screws **T** attaching the power / CD switch board and release the tab **e**.

# Removing the FL display & system control board

(See Fig. 22)

- 1. Disconnect the card wire from the connector UCW3, UJW5,UCW5 and UCW6 on the FL & System control board.

- 2. Remove the five screws **U** attaching the FL & System board.

- 3. Disconnect the card wire from the connector UCW2 on the FL & System control board.

#### ■Removing the front board (See Fig.23 to Fig.25)

- Prior to performing the following procedure, remove the FL display & System control board.

- 1. Pull out the VOLUME knob, ACTIVE BASS EX. LEVEL knob and SOUND MODE knob from front side.

- 2. Remove the eleven screws **V** attaching the front board and release the two tabs **f** out ward.

# Removing the headphone board & Mic jack board (See Fig.24)

- Prior to performing the following procedure remove the FL display & System control board.

- 1. You can pull out the headphone board.

- 2. Remove the mic jack board and release the tab g.

# Removing the cassette mechanism assembly (See Fig.25)

- 1. Disconnect the card wire  $\mathbf{x}$  from the mechanism board on the cassette mechanism assembly.

- 2. Remove the six screws  ${\bf W}$  attaching the cassette mechanism assembly.

#### MX-K55V

#### <CD changer unit>

· Prior to performing the following procedure, remove the CD changer unit.

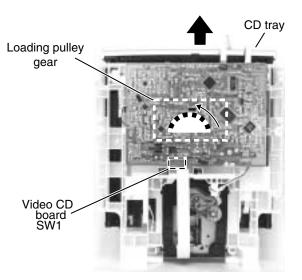

#### Removing the CD tray (See Fig.1 to 3)

- 1. Disconnect the card wire from connector SW1 of the video CD board.

- 2. Turn the biack loading pulley gear on the under side of the CD changer unit in the direction of the arrow and draw the CD tray toward the front until it stops.

- 3. Disconnect the card wire from connector CW6 of the Video CD board on the upper side of the CD changer unit.

- 4. Push down the two tray stoppers marked **a** and pull out the CD tray.

Fig.2

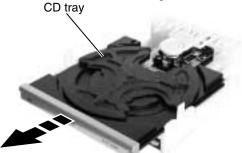

#### ■ Reinstall the CD tray (See Fig.4 and 5)

- 1. Align the gear-cam with the gear-tray as shown fig.4, then mount the CD tray.

- 2. When assembling the CD tray, take extreme care not engage with gear-synchro.

Gear-cam

Gear-convert

Gear-convert

Gear-tray

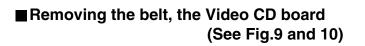

# Removing the sensor board / the turn table motor assembly (See Fig.6 to 8)

- Prior to performing the following procedure, remove the CD tray.

- 1. Remove the screw **A** attaching the sensor board and release the two tabs **b** attaching the sensor board on the under side of the CD tray.

- 2. Disconnect the harness from connector CW1 on the sensor board and release the harness from the two hooks **c**. Remove the sensor board.

- 3. Remove the screw **B** attaching the turn table. Detach the turn table from the tray.

- 4. Pull outward the tab marked **d** attaching the turn table motor assembly on the upper side of the tray and detach the turn table motor assembly from the tray.

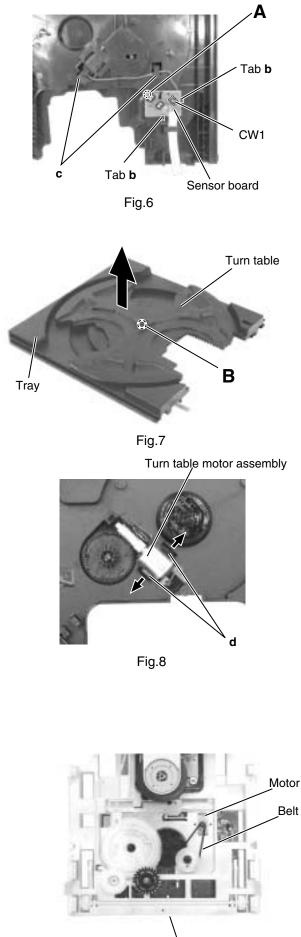

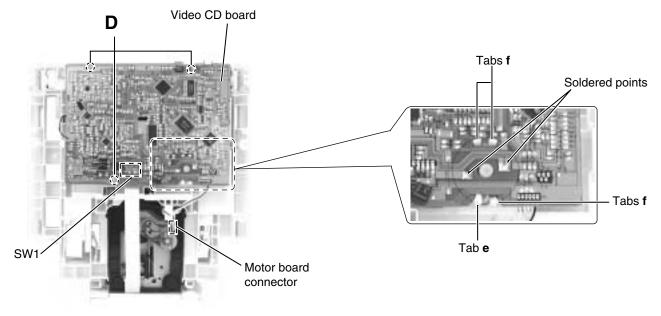

- Prior to performing the following procedure, remove the CD tray.

- 1. Disconnect the harness from connector on the CD mechanism board in the CD mechanism assembly on the under side of the CD changer unit. Disconnect the card wire from the pickup unit connector.

- 2. Detach the belt from the pulley on the upper side of the CD changer unit (Do not stain the belt with grease).

- 3. Disconnect the card wire from the connector SW1 on the Video CD board.

- ※ Remove the three screws D attaching the video CD board. First release the three tabs f and tabs e attaching the video CD board motor to raise the video CD board slightly, then release the video CD board.

If the tabs **e** and **f** are hard to release, it is recommendable to unsolder the two soldered points on the motor terminal of the video CD board.

Fig.9 CD changer unit

Fig.10

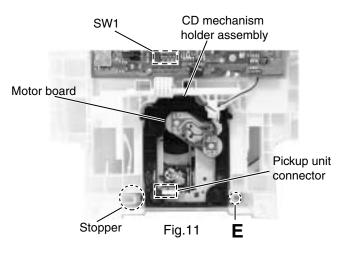

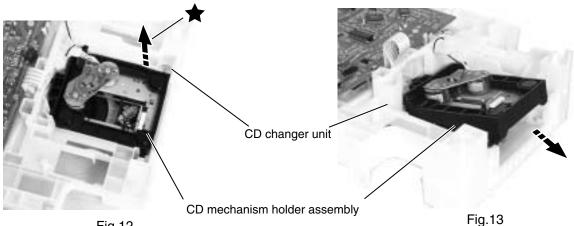

#### Removing the CD mechanism holder assembly (mechanism included) (See Fig.11 to 13)

- 1. Disconnect the card wire from pickup unit connector on the motor board in the CD mechanism holder assembly on the under side of the CD changer unit.

- 2. Remove the screw **E** attaching the shaft on the right side of the CD mechanism holder assembly.

- Pull outward the stopper fixing the shaft on the left side and remove the CD mechanism holder assembly from behind in the direction of the arrow ★.

- 4. Pull out the CD mechanism holder assembly.

Fig.12

#### <Cassette mechanism section>

• Prior to performing the following procedure, removing the cassette mechanism.

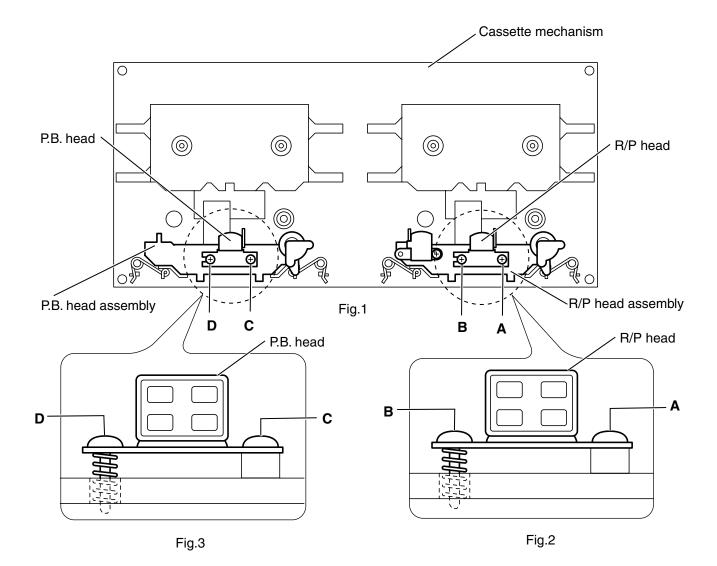

#### ■ Removing the R/P head. (Fig.1 to 3)

- 1. Remove the screw **A** attaching the R/P head right side.

- 2. Remove the screw **B** attaching R/P head left side. (Screw **B** : Head azimuth adjusting screw.)

#### ■ Removing the P.B. head. (Fig.1 to 3)

- 1. Removing the screw **C** attaching the P.B head right side.

- 2. Removing the screw **D** attaching the P.B head left side. (Screw **D** : Head azimuth adjusting screw.)

#### MX-K55V

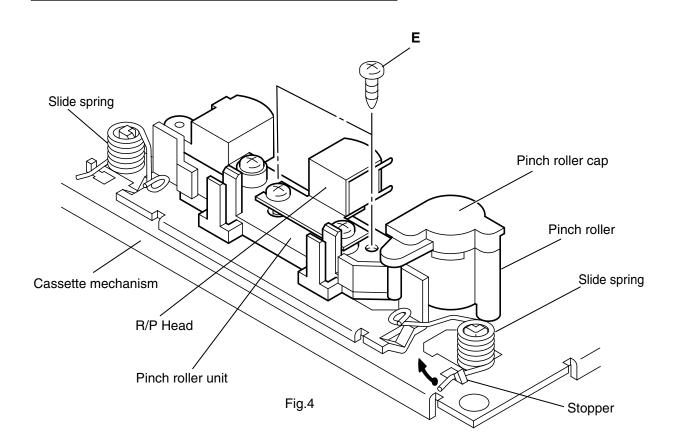

Removing the pinch roller unit.

(Fig. 4)

- Prior to performing the following procedure, removing the cassette mechanism.

- 1. Remove the two screws **E** attaching the pinch roller unit.

Attention:

The pinch roller cap is forcefully fitted to the shaft of the pinch roller unit. If the pinch roller cap is taken out by force, the shaft will be broken. When replacing the pinch roller, it should be changed as a pinch roller unit itself.

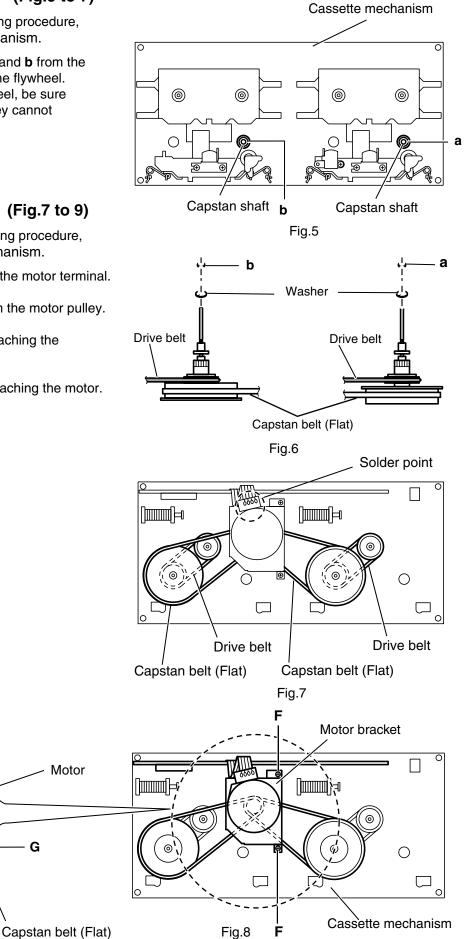

#### Removing the flywheel. (Fig.5 to 7)

- Prior to performing the following procedure, removing the cassette mechanism.

- 1. Remove the cut washers at **a** and **b** from the capstan shaft. Then remove the flywheel. When reassembling the flywheel, be sure to use new cut washers as they cannot be reused.

#### Removing the motor. (Fig.7 to 9)

- Prior to performing the following procedure, removing the cassette mechanism.

- 1. Unsolder the solder point on the motor terminal.

- 2. Remove the capstan belt from the motor pulley.

- 3. Remove the two screws F attaching the motor bracket.

Motor bracket

Capstan belt (Flat)

Fig.9

G

4. Remove the two screws G attaching the motor.

G

# Adjustment method

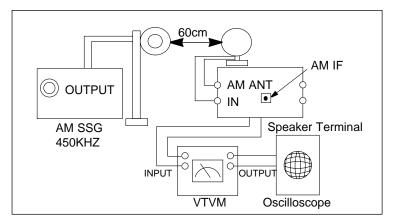

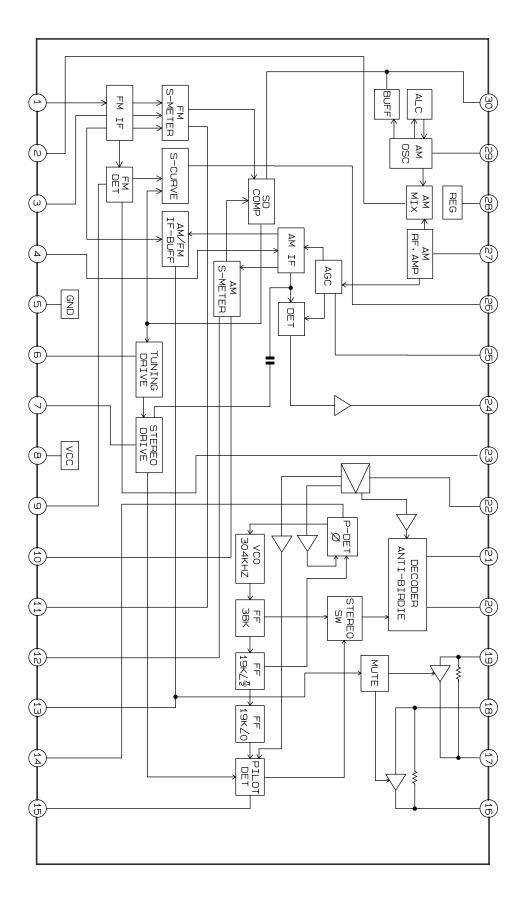

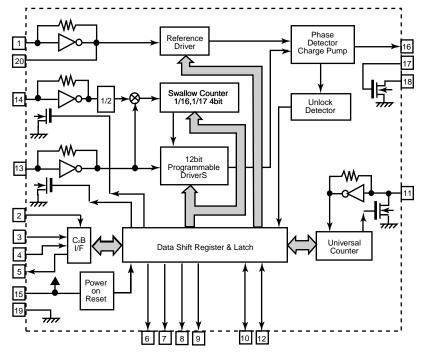

1. Tuner

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |   |

|--------------------------------------------------------|---|

|                                                        | _ |

\* Adjustment Location of Tuner board

| ITEAM               | AM(MW) OSC<br>Adjustment                                    | AM(MW) RF<br>Adjustment   | LW OSC<br>Adjustment<br>(Except for J/C) | AM(MW) RF<br>Adjustment   |

|---------------------|-------------------------------------------------------------|---------------------------|------------------------------------------|---------------------------|

| Received FREQ.      | 531~1602 KHz<br>(9kHz step)<br>530~1600 KHz<br>(10kHz step) | 594 KHz                   | 146~290 KHz                              | 150 KHz                   |

| Adjustment<br>point | MO                                                          | MA                        | LO                                       | LA                        |

| Output              | $1 \sim 7.0 \pm 0.5 V$                                      | Maximum<br>Output(Fig1-4) | 2~7.0 ±0.5 V                             | Maximum<br>Output(Fig1-4) |

Fig 1-4 OSC Voltage

#### MX-K55V

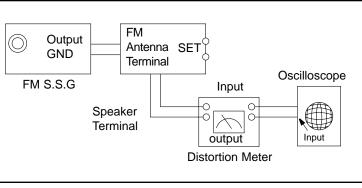

| FM                              | FM THD Adjustment  |  |  |  |

|---------------------------------|--------------------|--|--|--|

| SSG FREQ.                       | 98 MHz             |  |  |  |

| Adjustment<br>point<br>(FM DET) | FM DETECTOR COIL   |  |  |  |

| Output                          | 60 dB              |  |  |  |

| Minimum Disto<br>(Figure 1-1)   | rtion (0.4% below) |  |  |  |

Figure1-1 IF CENTER and THD Adjustment

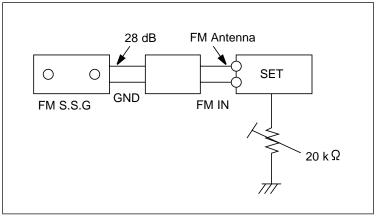

| 98 MHz                                                      |  |  |

|-------------------------------------------------------------|--|--|

|                                                             |  |  |

| AdjustmentBEACONpointSENSITIVITY(SVR1)SEMI-VR(20KΩ)         |  |  |

| 28 dB( ± 2dB)                                               |  |  |

| Adjust SVR1 so that "TUNED" of FL T is lighted (Figure 1-2) |  |  |

|                                                             |  |  |

\*Adjust FM S.S.G level to 28dB

Figure1-2 FM Auto Search Level Adjustment

| AM(MW) I.F Adjustment       |                                                   |  |

|-----------------------------|---------------------------------------------------|--|

| SSG FREQ.                   | 450 kHz                                           |  |

| Frequency                   | 531 kHz<br>(9kHz step)<br>530 kHz<br>(10kHz step) |  |

| Adjustment<br>point         | AM IF                                             |  |

| Maximum output (Figure 1-3) |                                                   |  |

Figure1-3 AM I.F Adjustment

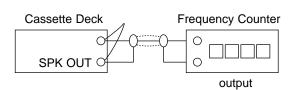

#### 2 Cassette Deck

#### To adjust tape speed

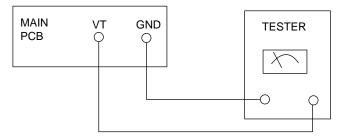

Notes 1) Measuring tape: i) VT-712 (Tapes recorded with 3kHz) ii) AC-225 2) Connect the cassette deck to the frequency counter as in figure 1-5.

Figure 1-5

| Step | ltem                    | Pre-Setup<br>Condition                            | Pre-Setup                                                                                             | To Adjust                                       | Standard | Remark       |

|------|-------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------|--------------|

| 1    | NOR<br>SPEED<br>Control | OUT<br>(connected<br>to the frequency<br>counter) | <ol> <li>Deck 1:VT-712</li> <li>Press PLAY<br/>SW button</li> <li>Deck 2:Same<br/>as above</li> </ol> | Turn VSR1 to<br>left and right<br>(FRONT board) | 3KHz     | ±1%<br>range |

Figure 1-8

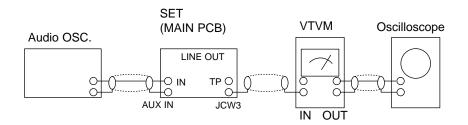

#### To adjust playback level/REC

Notes

Before the actual adjustment, clean the play/recording head.

Measuring tape :

i) VT-703 (10kHz AZIMUTH control)

ii) AC-225

The cassette deck is connections as shown in figure 1-7.

#### 1. Adjust Deck A Play Level

| Step | ltem    | Pre-Setup<br>Condition                            | Pre-Setup                                                            | To Adjust                                               | Standard                                        | Remark                                                   |

|------|---------|---------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|

| 1    | AZIMUTH | SPK OUT<br>(VTVM is<br>connected to<br>the scope) | After putting VT -<br>703 into Deck A<br>- Press FWD PLAY<br>button. | Turn the control<br>screw to as shown<br>in Figure 1-6. | Max output<br>and same phase<br>(both channels) | After<br>adjustment<br>secure it with<br>REGION<br>LOCK. |

#### 2. Adjust Deck B Play Level/REC BIAS

| Step | ltem                         | Pre-Setup<br>Condition                            | Pre-Setup                                                                                                   | To Adjust                                               | Standard                                        | Remark                                                   |

|------|------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|

| 1    | AZIMUTH                      | SPK OUT<br>(VTVM is<br>connected to<br>the scope) | After putting VT-703<br>into Deck B<br>1)Press FWD PLAY<br>button.                                          | Turn the control<br>screw to as shown<br>in Figure 1-6. | Max output<br>and same phase<br>(both channels) | After<br>adjustment<br>secure it with<br>REGION<br>LOCK. |

| 2    | Recording<br>Bias<br>Voltage | Fig 1-8                                           | After putting AC-225<br>into Deck B<br>1)Press REC PLAY<br>button.<br>2)MAIN PCB JCW3,<br>connected to VTVM | Turn JSR2L,JSR2R to the right and left                  | 7mV(±0.5mV)                                     |                                                          |

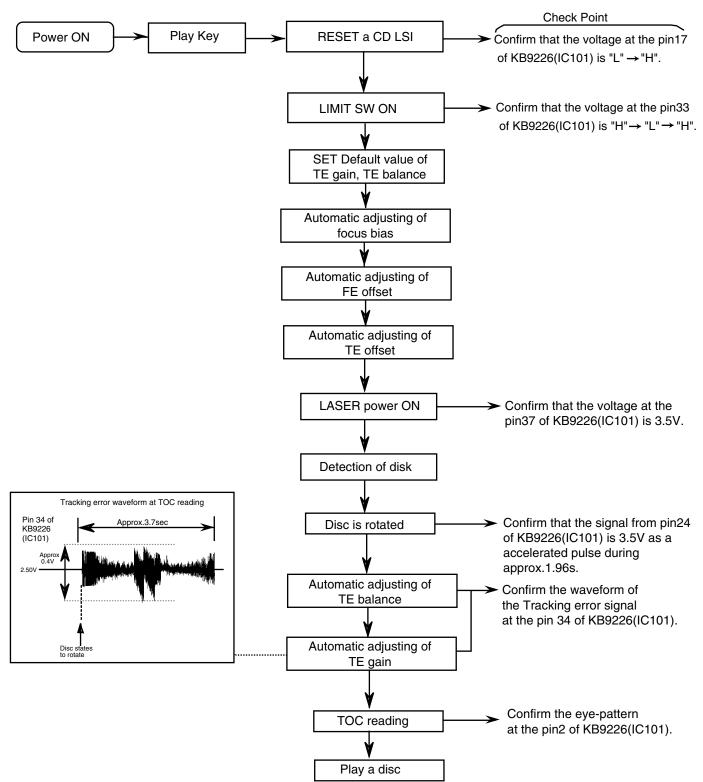

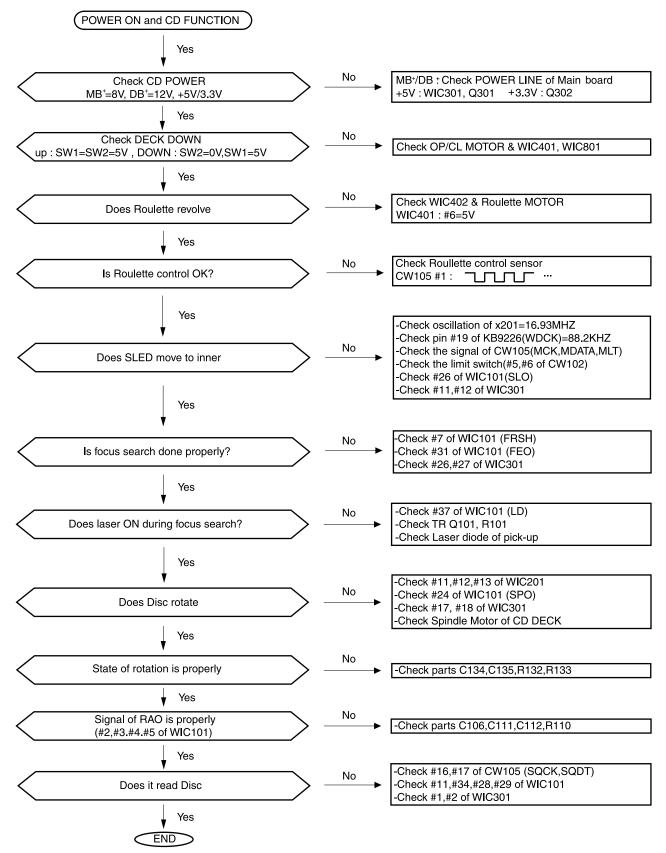

# Flow of functional operation until TOC read

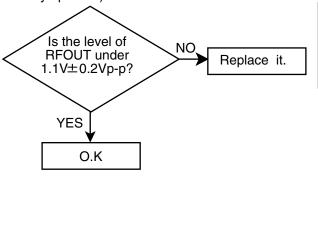

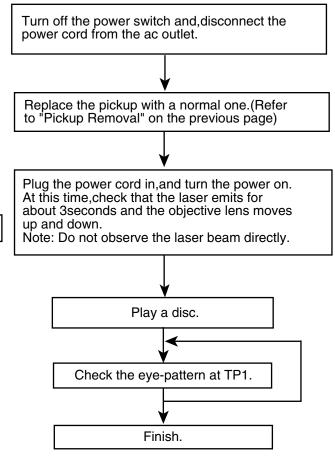

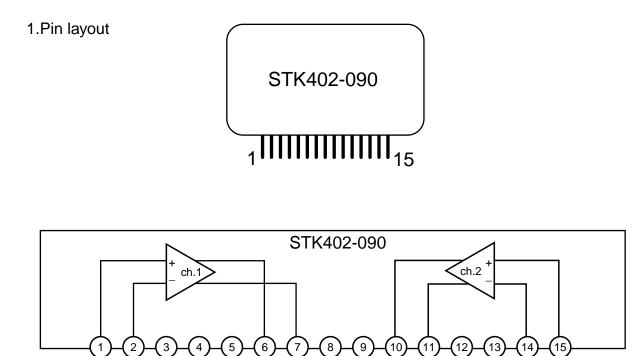

### Maintenance of laser pickup

- Cleaning the pick up lens Before you replace the pick up, please try to clean the lens with a alcohol soaked cotton swab.

- (2) Life of the laser diode When the life of the laser diode has expired, the following symptoms will appear.

- 1. The level of RF output (EFM output:ampli tude of eye pattern) will below.

(3) Semi-fixed resistor on the APC PC board

The semi-fixed resistor on the APC printed circuit board which is attached to the pickup is used to adjust the laser power. Since this adjustment should be performed to match the characteristics of the whole optical block, do not touch the semi-fixed resistor.

If the laser power is lower than the specified value, the laser diode is almost worn out, and the laser pickup should be replaced.

If the semi-fixed resistor is adjusted while the pickup is functioning normally, the laser pickup may be damaged due to excessive current.

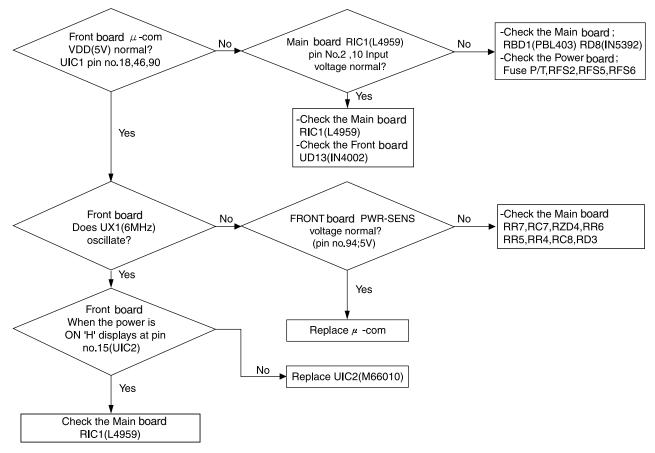

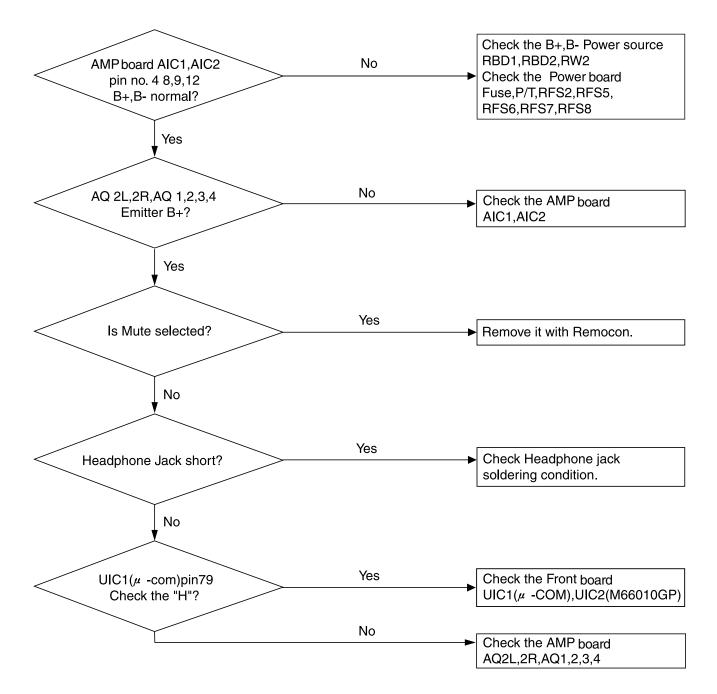

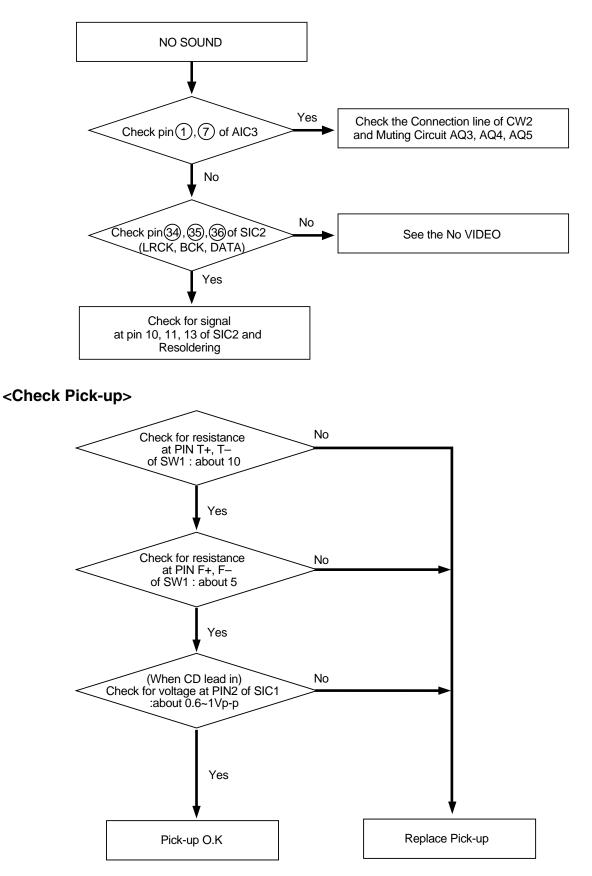

# Troubleshooting

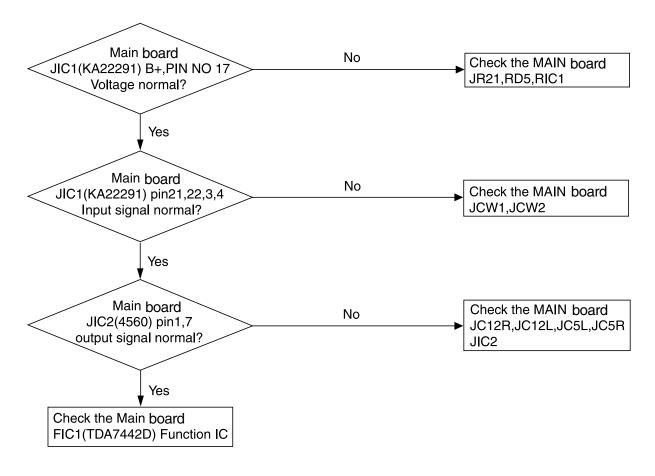

### **1.Amplifier**

#### **Power Malfunction**

#### <No Output>

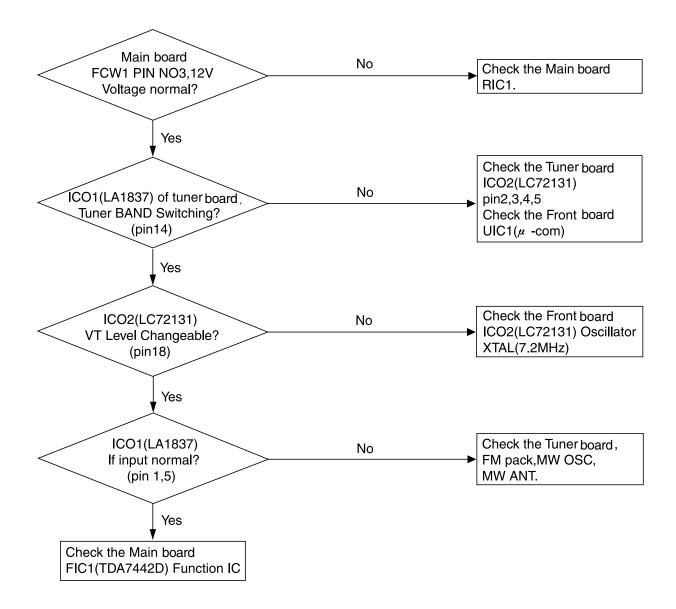

#### 2. Tuner malfunction (FM/AM)

#### 3. Tape

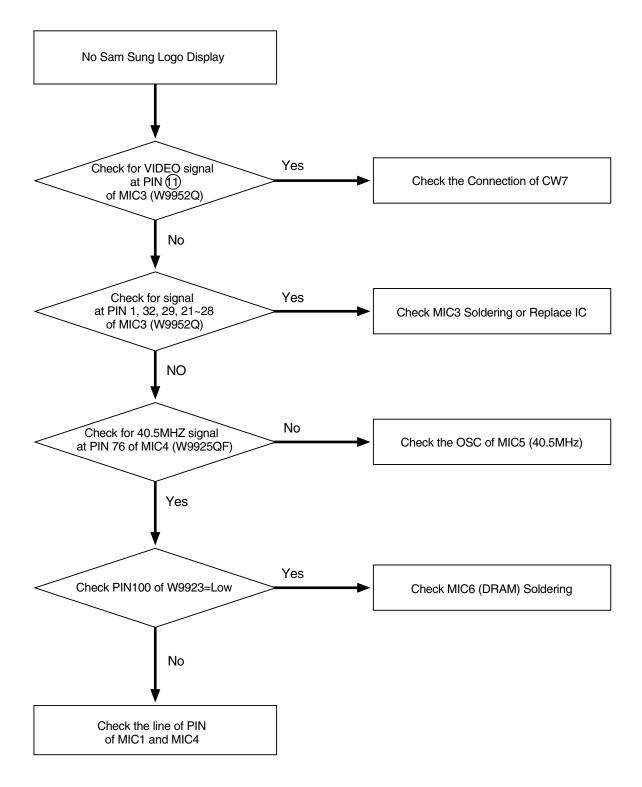

#### 4. Video CD

#### < No DISC>

#### <No VIDEO>

• Check the Voltage (+5V, +3.3V)

#### <No sound of CD Play>

- Check 16.9344MHz OSC at pin38 of MIC1

- Check Voltage (+5, ±12)

- Check all Connection between VCD pack board and Main, Front board

#### <3CD Tray does not close/open>

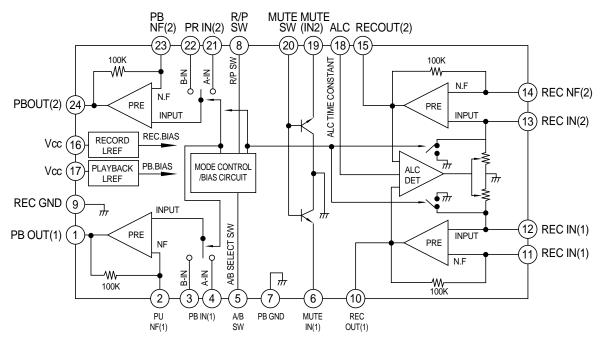

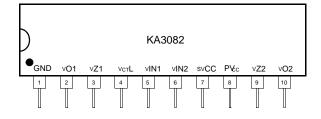

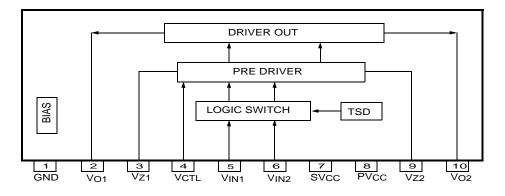

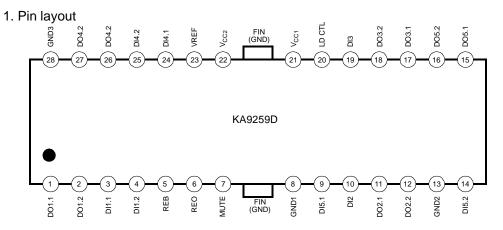

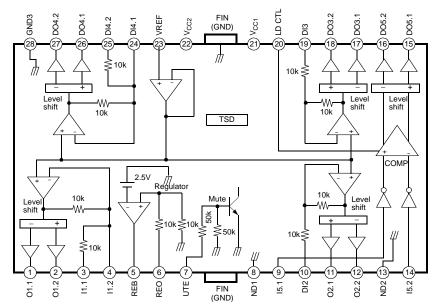

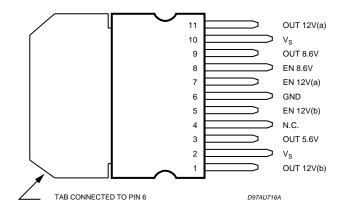

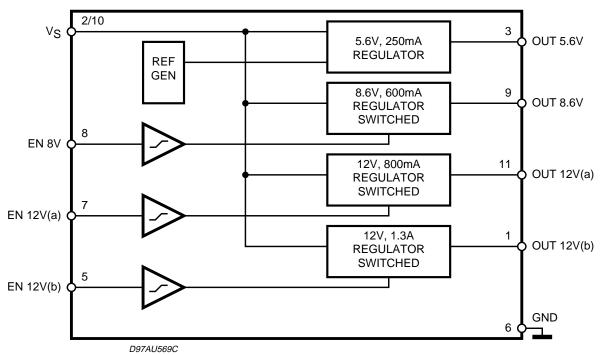

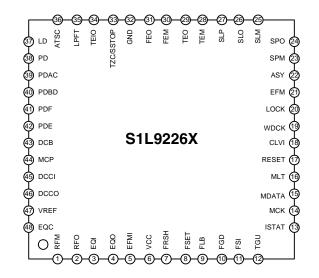

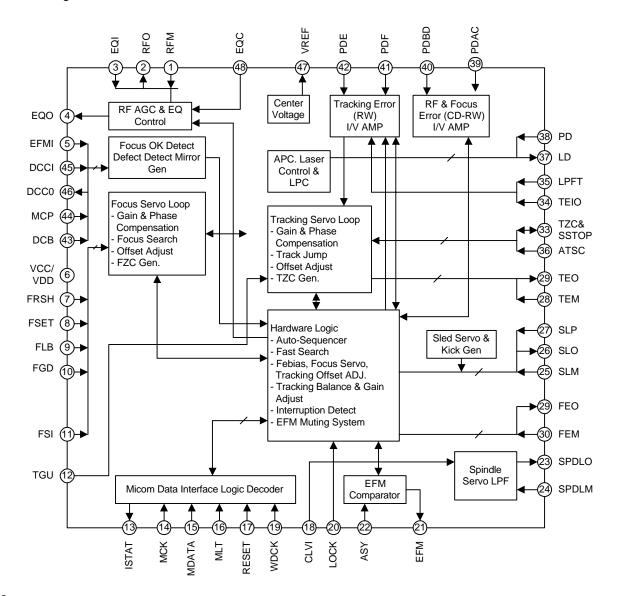

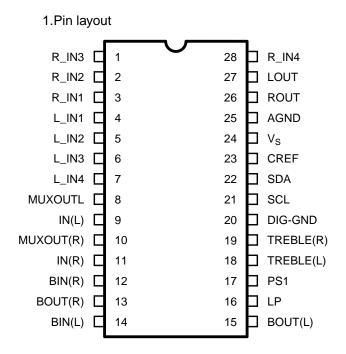

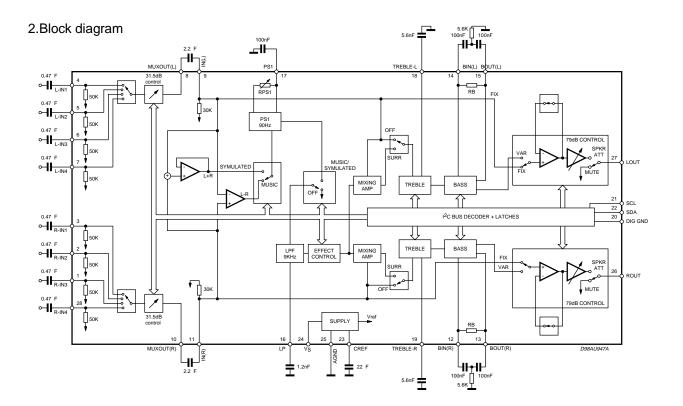

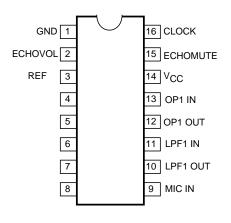

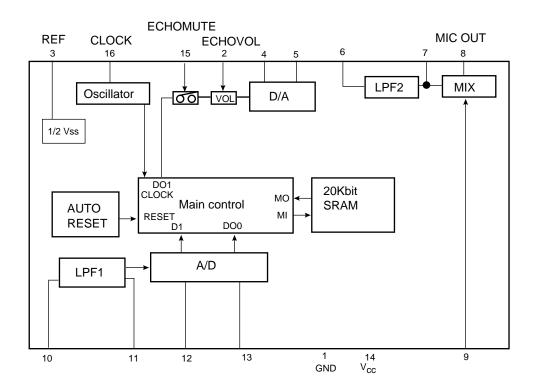

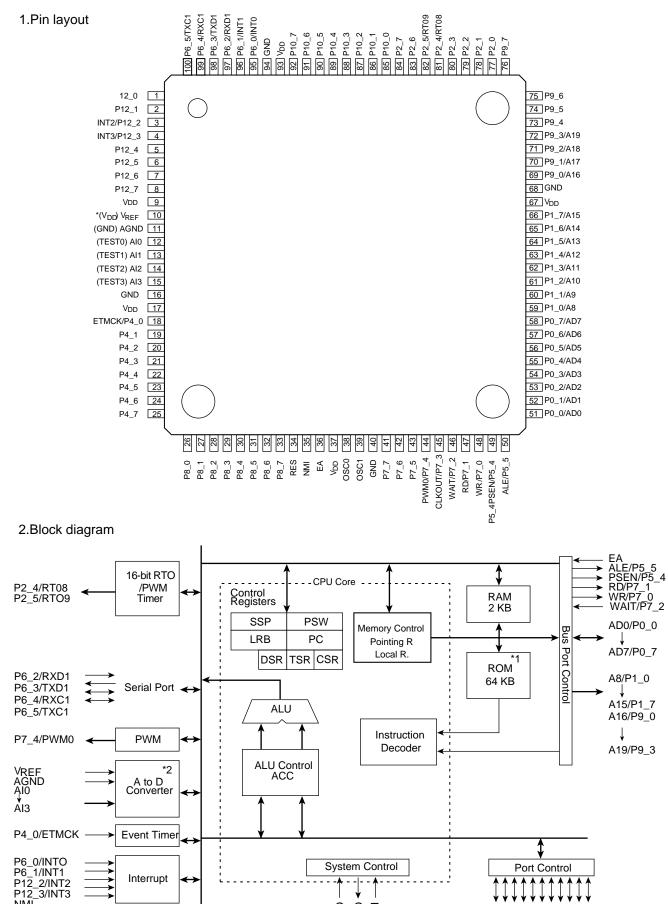

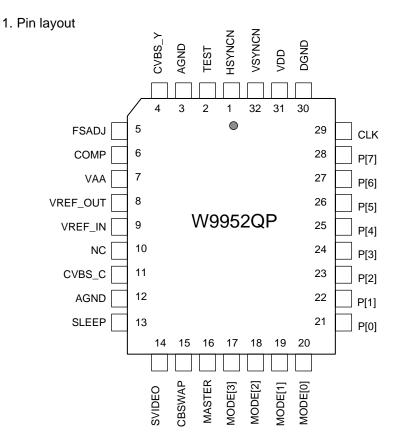

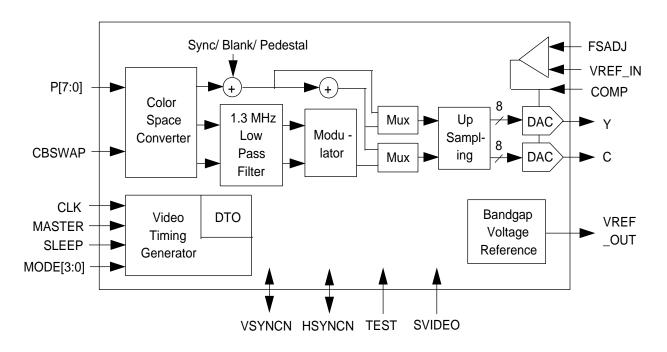

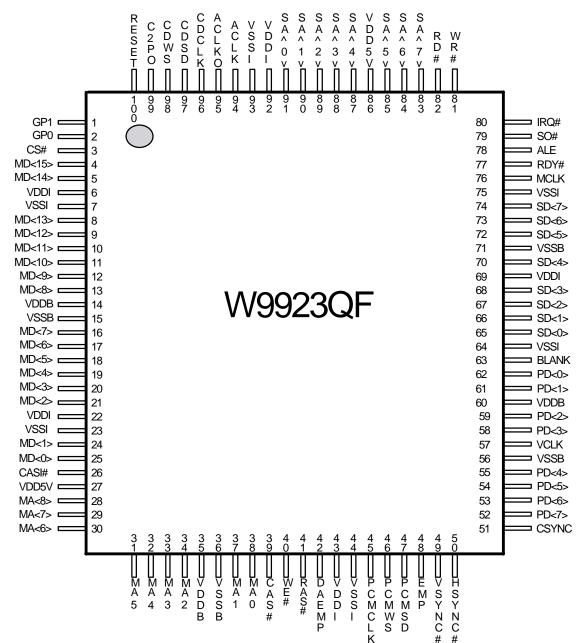

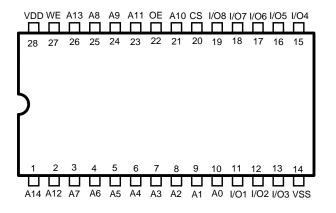

### **Description of major ICs**

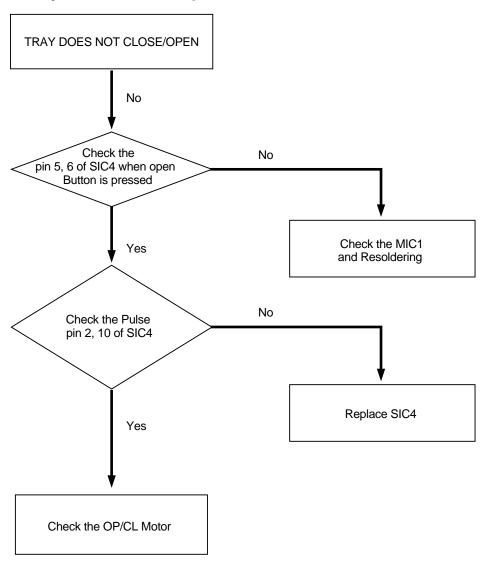

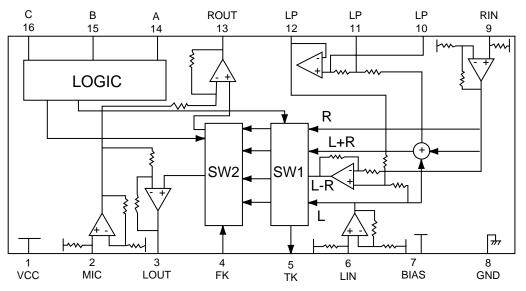

■ BA4560 (FIC2,FIC4,HIC1, JIC2,UIC3) : Dual op. amp.

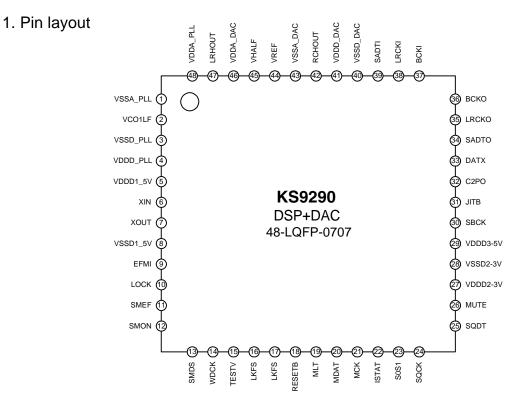

#### 1. Pin layout

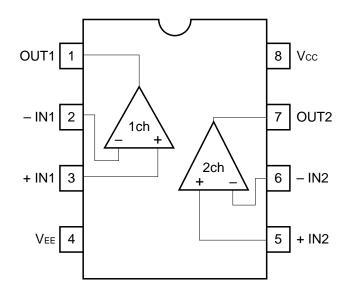

**STK402-090 (AIC1) : Power amp.**

CH1

IN

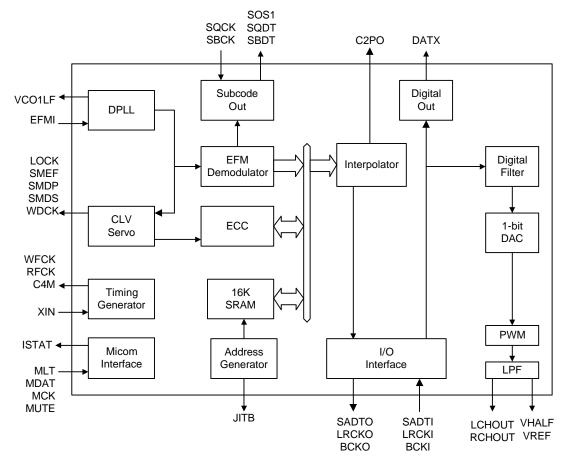

#### KS9290 (IC201) : Digital signal processor for CD player

#### 2. Block diagram

#### 3. Pin function

| Pin. No.         Symbol         Type         Function           1         VSSA_PLL         -         Analog Ground for DPLL           2         VCO1LF         O         Pump out for VCO1           3         VSSD_PLL         -         Digital Ground Separated Bulk Bias for DPLL (3V Power)           5         VDDD1-SV         -         Digital Power (SV Power, I/O PAD)           6         XIN         I         X'tal oscillator output           7         XOUT         O         X'tal oscillator output           8         VSSD1         -         Digital Ground (I/O PAD)           9         EFMI         I         EFM secontral output for Spindle Motor drive           10         LOCK         O         CLV Servo locking status output           11         SMEP         O         LPF time constant control of the Motor drive           14         WDCK         O         Word clock output (Normal Speed: 88.2KHz, Double Speed: 176.4KHz)           15         TESTV         I         Various Data/Clock Input           16         LKFS         O         The Lock status output of frame sync           17         C4M         O         4.2336MHz clock input           18         RESETB         I         Syst                                                         | 3. Pin fur | nction   |      | KS9290                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|------|---------------------------------------------------------------------|

| 2         VC01LF         0         Pump out for VC01           3         VSSD_PLL         Digital Ground Separated Bulk Bias for DPLL (3V Power)           5         VDDD PLL         Digital Power (SV Power, I/O PAD)           6         XIN         I         Xtal oscillator output (16.9344MHz)           7         XOUT         O         Xtal oscillator output           8         VSSD1         Digital Ground (I/O PAD)           9         EFMI         I         EFM signal input           10         LOCK         O         CLV Servo locking status output           11         SMEF         O         LPre time constant control of the spindle servo error signal           12         SMDP         O         Phase control output for Spindle Motor drive           13         SMDS         O         Speed control output for Spindle Motor drive           14         WDCK         O         Word clock output for Spindle Motor drive           15         TESTV         I         Various Data/Clock Input           16         LKFS         O         The Lock status output for Micom           21         MCK         I         Serial data receiving clock input form Micom           22         ISTAT         O         The internal status outp                              | Pin.No.    | Symbol   | Туре | Function                                                            |

| 3       VSSD_PLL       -       Digital Ground Separated Bulk Bias for DPLL         4       VDDD_FLL       -       Digital Power (SV Power, I/O PAD)         5       VDD1-5V       Digital Fower (SV Power, I/O PAD)         6       XIN       1       Xtal oscillator input (16.9344MHz)         7       XOUT       O       Xtal oscillator output         8       VSSD1       Digital Ground (I/O PAD)         9       EFMI       1       EFM signal input         10       LOCK       O       CLV Servo locking status output         11       SMEF       O       LPF time constant control of the spindle servo error signal         12       SMDP       O       Phase control output for Spindle Motor drive         13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       Word clock output for Spindle Motor drive         15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from                                                                                                     | 1          | VSSA_PLL | -    | Analog Ground for DPLL                                              |

| 4       VDDD_PLL       -       Digital Power (SV Power, I/O PAD)         5       VDD1-SV       -       Digital Power (SV Power, I/O PAD)         6       XIN       1       Xtal oscillator output (16.334MHz)         7       XOUT       O       Xtal oscillator output (16.944MHz)         8       VSSD1       -       Digital Ground (I/O PAD)         9       EFMI       I       EFM signal input         10       LOCK       O       CLV Servo locking status output         11       SMEF       O       LPF time constant control of the spindle servo error signal         12       SMDP       O       Phase control output for Spindle Motor drive         13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       Vord clock output (Normal Speed : 88.2KHz, Double Speed : 176.4KHz)         15       TESTV       I       Various Data/Clock output         16       LKFS       O       The Lock status output for firme sync         17       C4M       0       4.2330MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         22       ISTA                                                                                                    | 2          | VCO1LF   | 0    | Pump out for VCO1                                                   |

| 5     VDDD1-5V     -     Digital Power (5V Power, I/O PAD)       6     XIN     1     X'tal oscillator output       7     XOUT     O     X'tal oscillator output       8     VSSD1     -     Digital Ground (I/O PAD)       9     EFMI     1     EFM signal input       10     LOCK     O     CLV Servo locking status output       11     SMEF     O     LPF time constant control of the spindle servo error signal       12     SMDP     O     Phase control output for Spindle Motor drive       13     SMDS     O     Speed control output for Spindle Motor drive       14     WDCK     O     Word clock output (Normal Speed : 88.2KHz, Double Speed : 176.4KHz)       15     TESTV     I     Various Data/Clock Input       16     LKFS     O     The Lock status output of frame sync       17     C4M     O     4.2336MHz clock output from Micom       20     MDAT     I     Serial data input from Micom       21     MCK     I     Serial data receiving clock input from Micom       22     ISTAT     O     The internal status output to Micom       23     SOS1     O     Sub code-Q data rensferring bit clock input       24     SOCK     I     Sub code-Q data serial output <tr< td=""><td>3</td><td>VSSD_PLL</td><td>-</td><td>Digital Ground Separated Bulk Bias for DPLL</td></tr<> | 3          | VSSD_PLL | -    | Digital Ground Separated Bulk Bias for DPLL                         |

| 6       XIN       I       X'tal oscillator input (16.9344MHz)         7       XOUT       O       X'tal oscillator output         8       VSSD1       Digital Ground (I/O PAD)         9       EFMI       I       EFM signal input         10       LOCK       O       CLV Servo locking status output         11       SMEF       O       LPF time constant control of the spindle servo error signal         12       SMDP       O       Phase control output for Spindle Motor drive         13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       The Lock status output of frame sync         17       C4M       O       4.239MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         21       MCK       I       Serial data receiving clock input from Micom         22       ISTAT       O       The internal status output to Micom         23       SOS1       O       Sub code-Q data serial output         24       SQCK       I       Sub code-Q data serial output         25       SQDT       O       Sub code-Q data serial                                                                                                              | 4          | VDDD_PLL | -    | Digital Power Separated Bulk Bias for DPLL (3V Power)               |

| 7       XOUT       O       X'tal oscillator output         8       VSSD1       -       Digital Ground (I/O PAD)         9       EFMI       1       FFM signal input         10       LOCK       O       CLV Servo locking status output         11       SMEF       O       LPF time constant control of the spindle servo error signal         12       SMDP       O       Phase control output for Spindle Motor drive         13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       Word dock output (Normal Speed : 82.KHz, Double Speed : 176.4KHz)         15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       1       Latch signal input from Micom         21       MCK       1       Serial data receiving clock input from Micom         22       ISTAT       O       Sub code-Q data transferring bit clock input         24       SOCK       1       Sub code-Q data serial output         27       VDDD2                                                                                                    | 5          | VDDD1-5V | -    | Digital Power (5V Power, I/O PAD)                                   |

| 8         VSSD1         -         Digital Ground (I/O PAD)           9         EFMI         I         EFM signal input           10         LOCK         O         CLV Servo locking status output           11         SMEF         O         LPF time constant control of the spindle Motor drive           13         SMDS         O         Speed control output for Spindle Motor drive           14         WDCK         O         Word clock output (Normal Speed : 86.2KHz, Double Speed : 176.4KHz)           15         TESTV         I         Various Data/Clock Input           16         LKFS         O         The Lock status output of frame sync           17         C4M         Q         4.2336MHz clock output           18         RESETB         I         System Reset at 'L'           19         MLT         I         Latch signal input from Micom           20         MDAT         I         Serial data input from Micom           21         MCK         I         Serial data input from Micom           22         ISTAT         O         The internal status output for Micom           23         S0S1         O         Sub code-Q data transferring bit clock input           24         SQCK         I                                                          | 6          | XIN      | I    | X'tal oscillator input (16.9344MHz)                                 |

| 9       EFMI       I       EFM signal input         10       LOCK       O       CLV Servo locking status output         11       SMEF       O       LPF time constant control of the spindle servo error signal         12       SMDP       O       Phase control output for Spindle Motor drive         13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       Word clock output (Normal Speed : 88.2KHz, Double Speed : 176.4KHz)         15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         21       MCK       I       Serial data receiving clock input from Micom         22       ISTAT       O       The internal status output to Micom         23       SQS1       O       Sub code-Q data transferring bit clock input         24       SQCK       I       Sub code-Q data serial output         25       SQDT       O       Sub code data transferring bit clock                                                                                                | 7          | XOUT     | 0    | X'tal oscillator output                                             |

| 10       LOCK       O       CLV Servo locking status output         11       SMEF       O       LPF time constant control of the spindle servo error signal         12       SMDP       O       Phase control output for Spindle Motor drive         13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       Word clock output (Normal Speed : 86.2KHz, Double Speed : 176.4KHz)         15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         20       MDAT       I       Serial data input from Micom         21       MCK       I       Serial data receiving clock input from Micom         22       ISTAT       O       The internal status output to Micom         23       SOS1       O       Sub code-Q data transferring bit clock input         24       SQCK       I       Sub code and transferring bit clock input         25       SQDT       O       Sub code and transferring bit clock input<                                                                 | 8          | VSSD1    | -    | Digital Ground (I/O PAD)                                            |

| 11       SMEF       O       LPF time constant control of the spindle servo error signal         12       SMDP       O       Phase control output for Spindle Motor drive         13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       Word clock output (Normal Speed : 88.2KHz, Double Speed : 176.4KHz)         15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         20       MDAT       I       Serial data input from Micom         21       MCK       I       Sub code sync signal (S0-K1) output         23       SOS1       O       Sub code-Q data ransferring bit clock input         24       SQCK       I       Sub code-Q data ransferring bit clock input         25       SQDT       O       Sub code sync signal (S0+S1) output         26       MUTE       I       System mute at 'H'         27       VDDD2-3V       -       Digital Power (5V Power, I/O PAD)                                                                                            | 9          | EFMI     | I    | EFM signal input                                                    |

| 12       SMDP       O       Phase control output for Spindle Motor drive         13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       Word clock output (Normal Speed : 88.2KHz, Double Speed : 176.4KHz)         15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         20       MDAT       I       Serial data input from Micom         21       INCK       I       Serial data receiving clock input from Micom         22       ISTAT       O       The internal status output to Micom         23       S0S1       O       Sub code-Q data transferring bit clock input         26       MUTE       I       System mute at 'H'         27       VDD2-3V       Digital Power (3V Power, Internal Logic)         28       VSD2       -       Digital Cround (Internal Logic)         28       VDD3-5V       -       Digital audio data output         34       JATX                                                                                                       | 10         | LOCK     | 0    | CLV Servo locking status output                                     |

| 13       SMDS       O       Speed control output for Spindle Motor drive         14       WDCK       O       Word clock output (Normal Speed : 88.2KHz, Double Speed : 176.4KHz)         15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         20       MDAT       I       Serial data receiving clock input from Micom         21       MCK       I       Serial data receiving clock input from Micom         23       S0S1       O       Sub code synce signal (S0+S1) output         24       SQCK       I       Sub code synce signal (S0+S1) output         25       SQDT       O       Sub code synce signal (S0+S1) output         26       MUTE       I       System mute at 'H'         27       VDDD2-3V       Digital Power (SV Power, Internal Logic)         28       VSSD2       Digital Power (SV Power, I/O PAD)         30       SBCK       I       Sub code supt         32       C2PO       O       C2 point                                                                                                    | 11         | SMEF     | 0    | LPF time constant control of the spindle servo error signal         |

| 14       WDCK       O       Word clock output (Normal Speed : 88.2KHz, Double Speed : 176.4KHz)         15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         20       MDAT       I       Serial data input from Micom         21       MCK       I       Serial data receiving clock input from Micom         22       ISTAT       O       The internal status output to Micom         23       S0S1       O       Sub code-Q data transferring bit clock input         24       SQCK       I       Sub code-Q data serial output         25       SQDT       O       Sub code-Q data serial output         26       MUTE       I       System mute at 'H'         27       VDD03-5V       Digital Power (5V Power, I/O PAD)         30       SBCK       I       Sub code data transferring bit clock         31       JITB       O       Internal SRAM jitter margin status output         32       C2PO       O <t< td=""><td>12</td><td>SMDP</td><td>0</td><td>Phase control output for Spindle Motor drive</td></t<>           | 12         | SMDP     | 0    | Phase control output for Spindle Motor drive                        |

| 15       TESTV       I       Various Data/Clock Input         16       LKFS       O       The Lock status output of frame sync         17       C4M       O       4.2336MHz clock output         18       RESETB       I       System Reset at 'L'         19       MLT       I       Latch signal input from Micom         20       MDAT       I       Serial data receiving clock input from Micom         21       MCK       I       Serial data receiving clock input from Micom         23       S0S1       O       Sub code sync signal (S0+S1) output         24       SQCK       I       Sub code-Q data serial output         25       SQDT       O       Sub code-Q data serial output         26       MUTE       I       System mute at 'H'         27       VDDD2-3V       Digital Power (3V Power, Internal Logic)         28       VDD3-5V       -       Digital Power (5V Power, I/O PAD)         30       SBCK       I       Sub code data transferring bit clock         31       JITB       O       Internal SRAM jitter margin status output         32       C2PO       C2 pointer output       Gata output         33       DATX       O       Digital audio data outpu                                                                                                             | 13         | SMDS     | 0    | Speed control output for Spindle Motor drive                        |

| 16LKFSOThe Lock status output of frame sync17C4MO4.2336MHz clock output18RESETBISystem Reset at 'L'19MLTILatch signal input from Micom20MDATISerial data input from Micom21MCKISerial data receiving clock input from Micom22ISTATOThe internal status output to Micom23S0S1OSub code-Q data transferring bit clock input24SQCKISub code-Q data serial output25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDD2-3VDigital Power (3V Power, Internal Logic)28VSSD2-Digital Power (6V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKIIBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Power for DAC (3V Power)41VDD_DAG-Digital Power for DAC (3V Power)42RCHOUTOReference V                                                                                                                                                                                                                                                                                                                                      | 14         | WDCK     | 0    | Word clock output (Normal Speed : 88.2KHz, Double Speed : 176.4KHz) |

| 17C 4MO4.2336MHz clock output18RESETBISystem Reset at 'L'19MLTILatch signal input from Micom20MDATISerial data input from Micom21MCKISerial data receiving clock input from Micom22ISTATOThe internal status output to Micom23S0S1OSub code sync signal (S0+S1) output24SQCKISub code-Q data transferring bit clock input25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDDD2-3VDigital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data ransferring bit clock31JTBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output (48 slot, MSB first)34SADTOOSerial audio data input (48 slot, MSB first)35LRCK0OChannel clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DACDigital Power for DAC (3V Power)42RCHOUTOReference Voltage output torough DAC43VSSA_DACAnalog Ground for DAC44VREFO <td>15</td> <td>TESTV</td> <td>I</td> <td>Various Data/Clock Input</td>                                                                                                                                                                                                                                       | 15         | TESTV    | I    | Various Data/Clock Input                                            |

| 18RESETBISystem Reset at 'L'19MLTILatch signal input from Micom20MDATISerial data input from Micom21MCKISerial data receiving clock input from Micom22ISTATOThe internal status output to Micom23S0S1OSub code sync signal (S0+S1) output24SQCKISub code-Q data transferring bit clock input25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDDD2-3VDigital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output34SADTOOSerial audio data output35LRCKOOChannel clock output36BCKOOBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Ground for DAC43VSSA_DAC-Analog Ground for DAC44 <t< td=""><td>16</td><td>LKFS</td><td>0</td><td>The Lock status output of frame sync</td></t<>                                                                                                                                                                                                                                                                | 16         | LKFS     | 0    | The Lock status output of frame sync                                |

| 19MLTILatch signal input from Micom20MDATISerial data input from Micom21MCKISerial data receiving clock input from Micom22ISTATOThe internal status output to Micom23S0S1OSub code sync signal (S0+S1) output24SQCKISub code-Q data serial output25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDD2-3VDigital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Ground (Internal Logic)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output (48 slot, MSB first)34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Power for DAC (3V Power)41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTOReference Voltage output for bypass44VREFO<                                                                                                                                                                                                                                                                                                                             | 17         | C4M      | 0    | 4.2336MHz clock output                                              |

| 20MDATISerial data input from Micom21MCKISerial data receiving clock input from Micom22ISTATOThe internal status output to Micom23S0S1OSub code sync signal (S0+S1) output24SQCKISub code-Q data serial output25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDDD2-3VDigital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VSDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output (48 slot, MSB first)35LRCKOOBit clock output36BCKIIBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Power for DAC (3V Power)41VDDD_DAC-Digital Power for DAC43VSSA_DAC-Analog Ground for DAC44VREFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power f                                                                                                                                                                                                                                                                                                                                      | 18         | RESETB   | I    | System Reset at 'L'                                                 |

| 21MCKISerial data receiving clock input from Micom22ISTATOThe internal status output to Micom23SOS1OSub code-sync signal (S0+S1) output24SQCKISub code-Q data transferring bit clock input25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDDD2-3VDigital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output (48 slot, MSB first)35LRCKOOBit clock output36BCKOOBit clock input37BCKIIChannel clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Power for DAC41VDD_DAC-Digital Power for DAC43VSSA_DAC-Analog Ground for DAC44VREFOReference Voltage output through DAC45VHALFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC- <td< td=""><td>19</td><td>MLT</td><td>I</td><td>Latch signal input from Micom</td></td<>                                                                                                                                                                                                                                            | 19         | MLT      | I    | Latch signal input from Micom                                       |

| 22ISTATOThe internal status output to Micom23S0S1OSub code sync signal (S0+S1) output24SQCKISub code-Q data transferring bit clock input25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDD2-3V·Digital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V·Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output (48 slot, MSB first)34SADTOOSerial audio data output35LRCKOOBit clock output36BCKOOBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Power for DAC (3V Power)42RCHOUTOReference Voltage output for bypass45VHALFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                 | 20         | MDAT     | I    | Serial data input from Micom                                        |

| 23SOS1OSub code sync signal (S0+S1) output24SQCKISub code-Q data transferring bit clock input25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDDD2-3V-Digital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKIIBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSD_DAC-Digital Ground for DAC41VDD_DAC-Digital Power for DAC (3V Power)42RCHOUTOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                    | 21         | MCK      | I    | Serial data receiving clock input from Micom                        |

| 24SQCKISub code-Q data transferring bit clock input25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDDD2-3V-Digital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Ground (Internal Logic)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKIIBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDD_DAC-Digital Power for DAC (3V Power)42RCHOUTOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22         | ISTAT    | 0    | The internal status output to Micom                                 |

| 25SQDTOSub code-Q data serial output26MUTEISystem mute at 'H'27VDDD2-3VDigital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Power for DAC41VDD_DAC-Digital Power for DAC (3V Power)42RCHOUTOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23         | S0S1     | 0    | Sub code sync signal (S0+S1) output                                 |

| 26MUTEISystem mute at 'H'27VDDD2-3V-Digital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDD_DAC-Digital Power for DAC (3V Power)42RCHOUTORight-Channel audio output through DAC44VREFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24         | SQCK     | I    | Sub code-Q data transferring bit clock input                        |

| 27VDDD2-3V-Digital Power (3V Power, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output (48 slot, MSB first)34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock input38LRCKIIBit clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25         | SQDT     | 0    | Sub code-Q data serial output                                       |

| 21VSD2-SVDigital Fower (SV Fower, Internal Logic)28VSSD2-Digital Ground (Internal Logic)28VDD3-5V-Digital Power (SV Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock output37BCKIIBit clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26         | MUTE     | I    | System mute at 'H'                                                  |

| 28VDDD3-5V-Digital Power (5V Power, I/O PAD)30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTOReference Voltage output for bypass44VREFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27         | VDDD2-3V | -    | Digital Power (3V Power, Internal Logic)                            |

| 30SBCKISub code data transferring bit clock31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock input37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTORight-Channel audio output through DAC43VSSA_DAC-Analog Ground for DAC44VREFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28         | VSSD2    | -    | Digital Ground (Internal Logic)                                     |

| 31JITBOInternal SRAM jitter margin status output32C2POOC2 pointer output33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock output37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTORight-Channel audio output through DAC43VSSA_DAC-Analog Ground for DAC44VREFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28         | VDDD3-5V | -    | Digital Power (5V Power, I/O PAD)                                   |

| 32C2POOC2 pointer output33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock output37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTORight-Channel audio output through DAC43VREFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30         | SBCK     | I    | Sub code data transferring bit clock                                |

| 33DATXODigital audio data output34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock output37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTORight-Channel audio output through DAC43VSSA_DAC-Analog Ground for DAC44VREFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31         | JITB     | 0    | Internal SRAM jitter margin status output                           |

| 34SADTOOSerial audio data output (48 slot, MSB first)35LRCKOOChannel clock output36BCKOOBit clock output37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTORight-Channel audio output through DAC43VSSA_DAC-Analog Ground for DAC44VREFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32         | C2PO     | 0    | C2 pointer output                                                   |

| 35LRCKOOChannel clock output36BCKOOBit clock output37BCKIIBit clock input38LRCKIIChannel clock input39SADTIISerial audio data input (48 slot, MSB first)40VSSD_DAC-Digital Ground for DAC41VDDD_DAC-Digital Power for DAC (3V Power)42RCHOUTORight-Channel audio output through DAC43VSSA_DAC-Analog Ground for DAC44VREFOReference Voltage output for bypass45VHALFOReference Voltage output for bypass46VDDA_DAC-Analog Power for DAC (3V Power)47LCHOUTOLeft-Channel audio output through DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33         | DATX     | 0    | Digital audio data output                                           |